| 现场环境 |

在半导体集成电路封装车间内,键合引线在生产过程中容易受到设备状态波动、工艺不稳定等因素的影响,出现各种缺陷。检测环境需要能够适应工业生产中的复杂条件,如不同的光照强度、噪声干扰 |

| 使用对象 |

半导体键合引线,包括引线的连接点、引线的形状和结构 |

| 使用目的 |

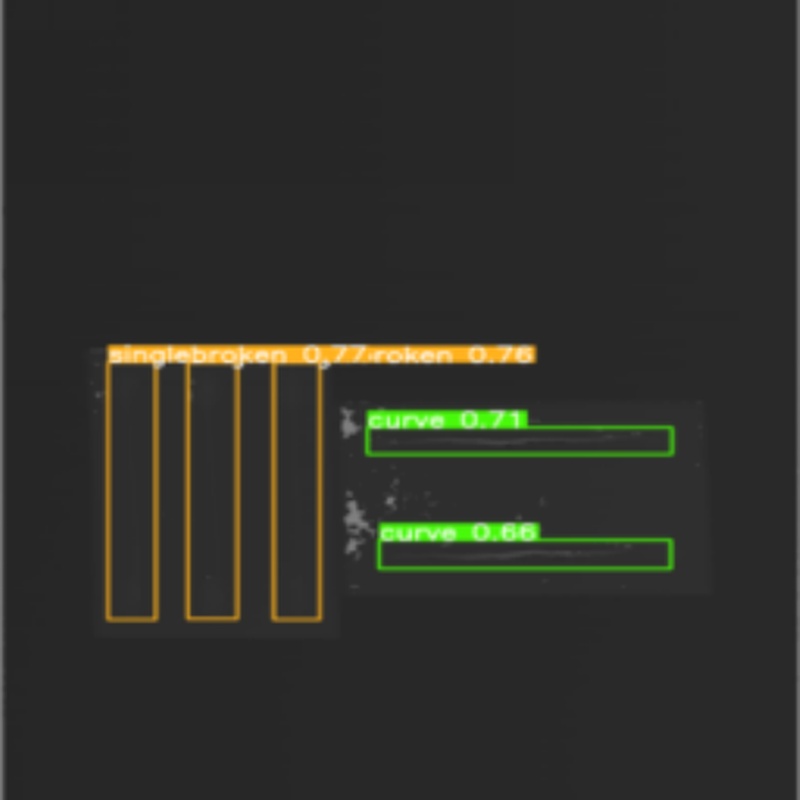

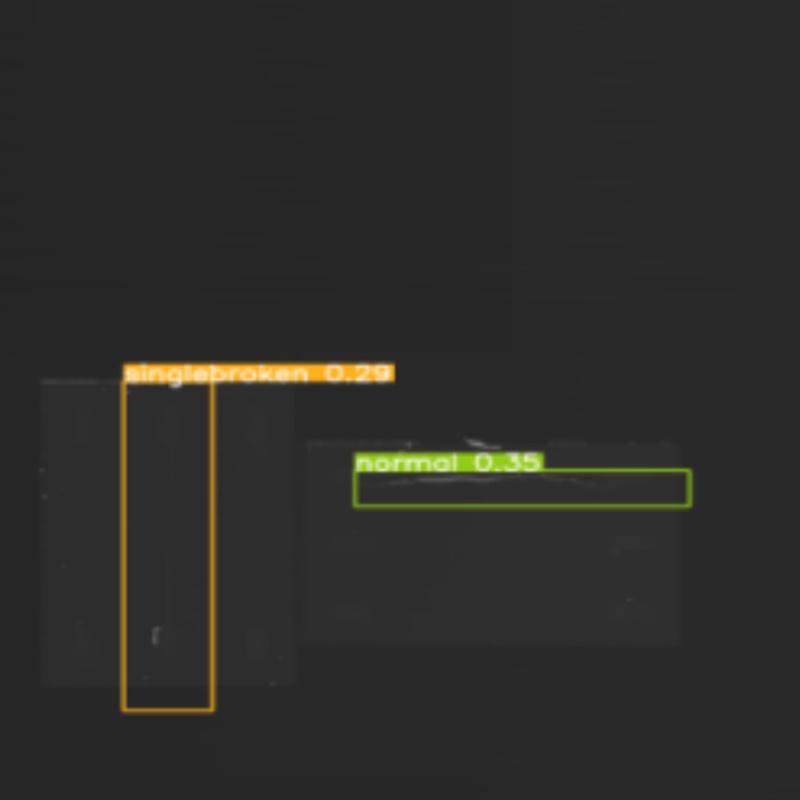

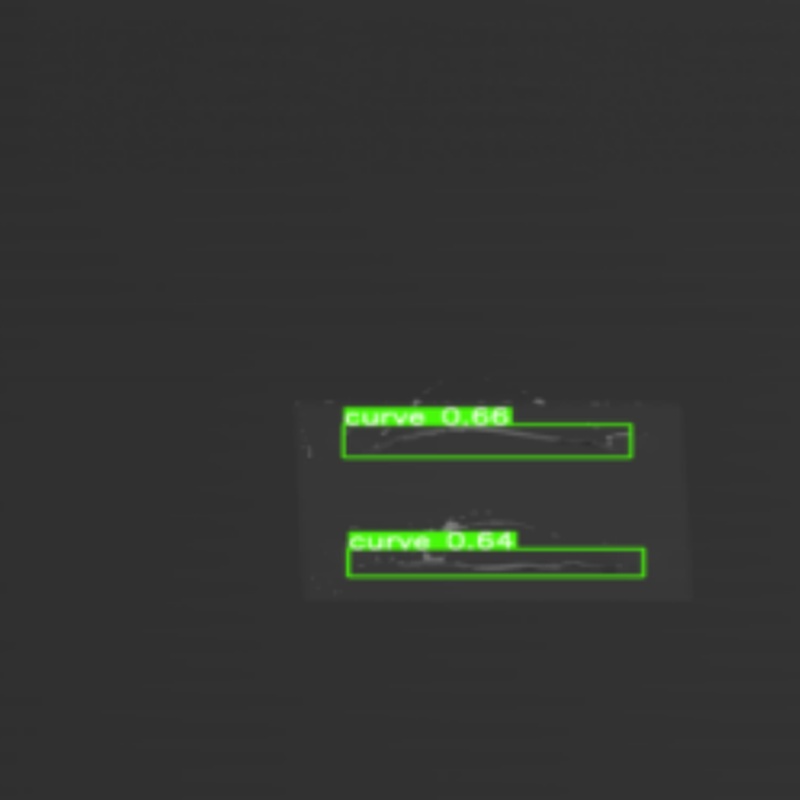

准确检测键合引线的缺陷,如双线干涉、引线桥接、中间断线、单端断线、弧度异常、线弯曲、尾丝过长等,提高产品质量和生产效率,降低生产成本。 |

| 硬件配置 |

CPU:Intel (R) Core (TM) i7-12700k

GPU:NVIDIA RTX 3090,显存24GB

内存:64GB

硬盘:未明确提及,但应具备足够的存储空间

网卡:未明确提及,但需满足数据传输需求

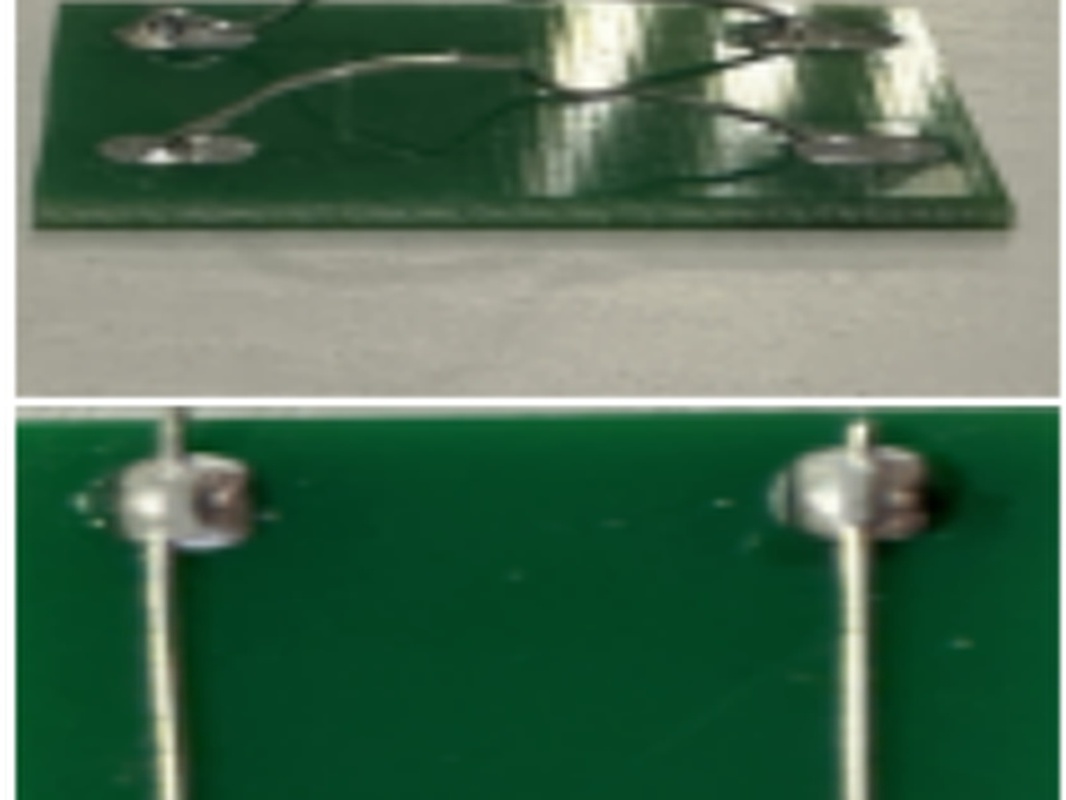

摄像头:海康威视线结构光相机(MV-DP2307-01H),用于采集深度图像

运动滑轨平台:有效行程10-1400mm,丝杆精度0.03mm,垂直载重15kg

运动控制器:DM542步进电机驱动器 |

| 硬件兼容 |

无

|

| 软件配置 |

操作系统:Ubuntu 20.04

编程语言:Python 3.8

深度学习框架:PyTorch 2.10

图形加速:CUDA 12.1 |

| 软件兼容 |

无

|

| 输入数据 |

键合引线的深度图像,图像分辨率为640×640像素,以TIFF格式存储。通过将单通道深度图像与三通道法线图像堆叠,生成四通道的伪RGB-D图像作为模型输入。 |

| 输出数据 |

:缺陷类型(双线干涉、引线桥接、中间断线等)、缺陷位置坐标(以图像像素坐标表示)、置信度。 |

| 样本获取 |

通过搭建的键合引线缺陷数据采集物理平台,采集了键合引线的深度图像。共采集到2000张原始深度图像,经过预处理和数据增强后,生成了包含10000张图像的数据集DepthBondingWire。其中6000张用于训练集,4000张用于测试集。 |

| 测试结果 |

在自建数据集DepthBondingWire上,Depth-YOLO模型的mAP@0.5达到了98.6%,相比于原始YOLOv8模型提升了7.2%。与其他主流目标检测模型相比,Depth-YOLO在检测精度上具有明显优势。 |

| 执行速度 |

检测速度约50ms/次 |

| 资源消耗 |

CPU:在多核CPU上,计算占比分别平均约50%、60%、70%、40% GPU:显存占用约6GB,显卡计算占比约80% 内存:使用占比约60% |

| 源码类型 |

本算法有Python版本源码,可提供授权使用。 |

| 文件大小 |

算法程序文件约16K,权重文件约34M。 |

| 相关备注 |

无 |